本篇承接上两篇文章,继续介绍DDR内存在固件中如何初始化,以及如何提高初始化的效率等等。

小张上次回去后,好久都没来找我,我以为他对内存知识已经不感兴趣了,没想到他今天又约我见面。我来到上次的咖啡馆,他已经等我好久了。原来他上次回去后,找了好久资料,虽然对硬件知识有了个整体的把握,但看的越深入就有越多的疑问。他知道我对固件了解比较深入,想问问我关于软件方面的问题。我不禁被小张对知识的渴求所打动,点了一杯美式咖啡,开始了今天的介绍。

内存初始化

小张开门见山,直奔主题:“内存硬件结构这么复杂,我平时写程序怎么从来都没有用过,是不是操作系统把什么寻址啊、延迟啊都自己搞定了?”。“这就不对了,操作系统对内存的了解只到了段页管理那一层,也就是到了物理地址那里。你可以看看我的博客,上面有介绍段页管理。物理地址到Rank,Bank等的寻址,都是内存控制器完成的。”我喝了一口咖啡,开始津津有味的介绍起来。

自Intel/AMD把北桥取消后,内存控制器都被集成进了CPU,毕竟摆脱了FSB,延迟大大减小,而带宽可以大大增加,同时主板的成本也降低了。初始化内存控制器和内存是固件的一项重要任务,可以说是主要任务之一。也许你看过前面关于UEFI的介绍,就会明白,内存初始化是在PEI阶段完成的。一般来说我们把内存初始化分成三个阶段:

1。准备阶段

这个阶段主要是为了内存training做好准备。它要完成:

A. 初始化内存控制器寄存器。

B. 读取SPD内容。通过SMBUS读取SPD的内容,对各个延迟记录在案,下个阶段会用到。各个DIMM的SMBUS地址不同,一般是A0/A1/A2/A3,和主板走线有关。这个步骤也可以检查出来内存插槽上有没有插DIMM。在有些嵌入式主板上内存颗粒是直接焊到主板上的,这时很可能没有SPD。这时就需要固件工程师根据实际的内存颗粒的硬件手册,将延迟信息硬编码到代码中了。

2。内存Training

看到Training也许你会感到奇怪,人工智能是要训练,内存也要训练吗?

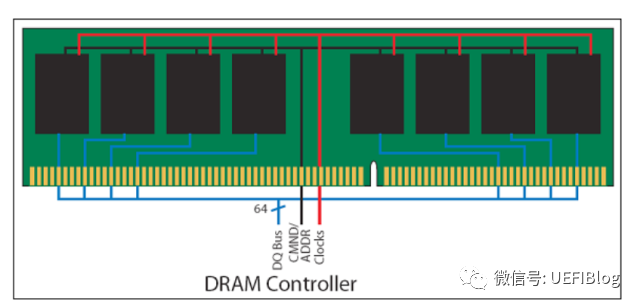

从DDR2到DDR3,一个很大的改动是信号线的连接方式。一个典型的DDR2的连接方式如图:

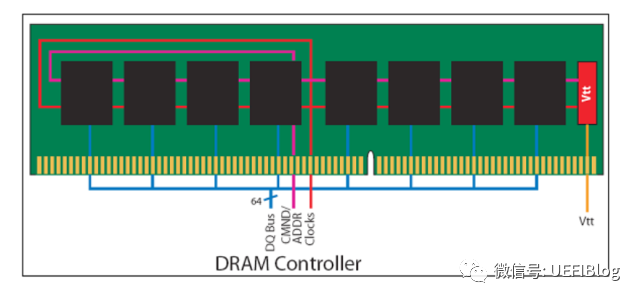

而DDR3变成:

这种菊花链式的方式,DDR标准的制定者JEDEC对它有个专门的叫法——“Fly-by”。这种设计大大减小DIMM厂商的硬件制造难度。同时由于CLK/CLK#、DQS、AD和CMD信号不需要同时传递,改善了信号完整性,使更高频率成为可能。世界上没有免费的午餐,它也带了不少麻烦,一个很大的问题是内存控制器的时序协调难度变大了很多。菊花链的连接方式也意味着信号在各个内存颗粒之间传递有个时间差。第一个内存颗粒和第二个颗粒也许延迟不大,但到了第八个就相当可观了。回忆一下我们上次的介绍,在行有效和列有效后,过了CL的时间第一颗chip把数据放在数据线DQ相应位上,而要过了很久第八颗Chip才把数据准备好,内存控制器要何时才能采集数据呢?现在每个内存通道一般都有两个内存插槽,情况会更加复杂。火上浇油的是,DDR标准是JEDEC制定的,内存颗粒和DIMM厂商是个生态圈,里面鱼龙混杂,内存颗粒和DIMM的延迟千奇百怪。这和ARM做的嵌入式平台只需要支持固定的内存颗粒完全不同,所有主板厂商都希望支持市面上更多的内存条。有时这就像踩钢丝,对内存A很好的时序,也许对内存B就不行。如果在启动阶段就发现时序错误还好,错误或者过激的时序如果躲过了BIOS的内存检测,到了操作系统运行的时候会造成更大的麻烦。

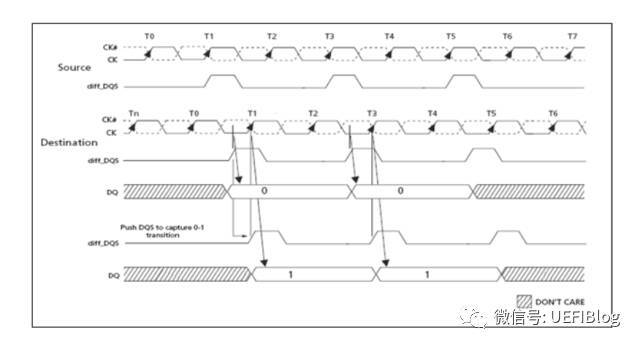

如何才能准确的设定时序呢?所幸JEDEC提供了标准做法,叫做Write Leveling Coarse。简单来说,就是内存控制器不停的发送不同时延的DQS 信号,内存 颗粒在DQS-DQS#的上升沿采样CK 的状态,并通过DQ 线反馈给DDR3 控制器(一组01010101的数据)。控制器端反复的调整DQS-DQS#的延时,直到控制器端检测到DQ 线上0 到1 的跳变控制器就锁住此时的延时值,此时便完成了一个Write leveling过程。如下图:

它结合其他的如on-die termination (ODT)和调节Vref电压等一起完成了内存的Training。这是个不断找到平衡点的过程,也是个训练内存控制器了解DIMM的Timing和电压的过程。

3。扫尾阶段

假定上个阶段成功的发现并设置了参数,下面就比较简单了。主要是设置Channel和Interleave,将结果报告给固件的其他部分了。这里有许多信息比较有趣,有内存的厂家、具体型号、数量多寡、内存条和内存插槽的配合情况,多CPU还有内存的亲缘性关系等等,这些信息会被放入HOB中以备以后调用。

其他

滔滔不绝讲了半天,心想这些够小张喝一壶了吧。我满意的喝了口咖啡,没想到小张从口袋里拿出来个A4纸,上面密密麻麻好多问题。好小子,前面装傻,在这里等着我呢。没关系,兵来将挡,水来土掩,尽管放马过来吧!

1。如何得到源码

“听了半天,似乎听懂了,有没有代码看看呢? Talk is cheap, show me the code!”。内存初始化代码一般由芯片厂商提供,Intel管它叫MRC(memory reference code)。因为其中涉及大量的寄存器操作,一般采取授权访问的方式提供给IBV和OEM而不是open source。所幸Intel的开源硬件平台伽利略(Galileo)开放了SOC Quark的所有源代码,包括MRC代码,它在:

tianocore/edk2

有兴趣的同学可以去学习一下。

2。CAR

“我看内存初始化之前,UEFI已经在执行c程序了。这时堆栈在哪里呢?”。好问题,在内存准备好之前。UEFI固件一般把cache初始化为内存(CAR, Cache As Ram)。不但如此,我们还可以把一部分cache拿来继续做cache用,缓存数据和代码,而且被用作内存的cache还可以执行代码!Cache可真是强大啊!

3。Fast boot/S3

“内存初始化要训练,感觉很慢,有没有办法加速呢?”。有的,如果我们没有更换内存条,我们其实没有必要每次都从头开始训练。我们可以把第一次开机训练的内存数据存储下来,以后用前面的数据就行了,这就是很多BIOS内存部分的Fast Boot。

“那我要是换了内存呢,会死机吗?“。不会的,主板有个GPIO连接到机箱开关上,我们打开机箱,BIOS会捕捉到这个信息(叫做Intrude)。利用这个信号,我们可以认为用户做了些改变配置的事,我们在从头训练就好了。有的MRC还会在SPD信息改变后自动重新训练。

“能讲讲休眠模式下内存的设置吗?”。S3,也就是Sleep to memory,是ACPI规定的一种休眠模式,具体我们以后再讲(再挖个坑有没有?)。这里我就简单说下内存的状态。一般SDRAM都要刷新,这是由它的设计决定的,它有个特殊的模式,叫做自刷新,在这个模式下,内存内容不会消失而且耗电极小。我们的S3就是把内存设置成这种状态。

4。如何设置各种延迟

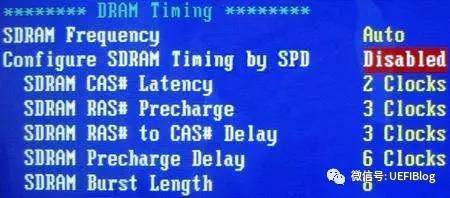

“我能改变上次说的那些延迟参数吗?”。BIOS一般会根据SPD自动设置各种延迟,我们也可以在BIOS设置中自行设置这些参数,如下图:

但是设置要小心,错误的改动有可能会造成启动不了,确定你改动这些设置之前知道怎么清除CMOS或者重置BIOS。